丁华俊 薛忠营 魏星 张波

(中国科学院上海微系统与信息技术研究所,高端硅基材料与器件实验室,上海 200050)

通过引入1 nm 铝作为插入层,研究了铝在调制镍与n 型锗反应时对镍化锗与n 型锗接触的肖特基势垒高度的影响.采用正向 I-V 法、Cheung 法和 Norde 法分别提取了镍化锗与n 型锗接触的肖特基二极管的串联电阻、势垒高度和理想因子.研究表明,在镍和锗衬底之间引入1 nm 铝插入层,能够有效降低势垒高度,且其能够在 350 ℃—450 ℃ 保持稳定.

随着超大规模集成电路发展到纳米节点,硅(Si)材料逼近其物理极限,短沟道效应、隧穿效应等对器件性能的影响愈发严重.为了维持摩尔定律,需要新材料、新工艺和新结构来实现晶体管尺寸的进一步缩小.锗(Ge)由于具有超高的电子和空穴迁移率被认为是下一代高迁移率互补金属氧化物半导体(complementary metal oxide semiconductors,CMOS)器件中具有前景的沟道材料[1,2].Ge 价带附近的费米能级钉扎增加了通过选择具有不同功函数的金属来调节金属和锗之间的势垒高度的难度,这也是实现高性能锗基CMOS 器件的主要挑战之一[3].国内外学者均提出使用插入层来调节金属与Ge 接触势垒高度.Jason等[4]提出使用二氧化钛界面层降低金属与n 型Ge 接触的肖特基势垒高度,增加电流密度.Lieten等[5]提出使用氮化锗作为界面层抑制金属与n 型Ge 接触的费米能级钉扎,可以在n 型Ge 上形成欧姆接触,在p 型Ge 上形成整流接触.Liu等[6]提出氟化石墨烯中间层能够有效地缓解钛与n 型Ge 接触的肖特基二极管(Schottky barrier diode,SBD)中费米能级钉扎的现象,并且其势垒高度与偏置电压无关.Kobayashi等[7]提出使用氮化硅界面层能调制金属与n 型Ge 接触的肖特基势垒高度.Lin等[8]提出使用超薄氧化铝界面层来调制金属与n 型Ge 接触的肖特基势垒高度,可以降低接触电阻.

在传统的体硅工艺中,自对准硅化物可用于源/漏接触和局部互连,自对准锗化物可应用于锗基器件的制造,镍化锗 (NiGe)具有低电阻率、低形成温度和兼容自对准工艺,是最有潜力的候选材料之一,但是,NiGe 因为热稳定性较差,在高温下会严重影响器件的性能[9,10].目前,国际上大多使用金属插入层来提高NiGe 热稳定性,比如使用Ti[11]等.

本文提出使用超薄的铝(Al)插入层调制NiGe/n-Ge SBD,基于热离子发射模型,采用正向I-V法,Cheung 的方法和 Norde 的方法提取肖特基势垒参数,结果表明,经过1 nm Al 调制后的NiGe/n-Ge SBD 的肖特基势垒高度有所降低,在 350—450 ℃ 保持稳定.

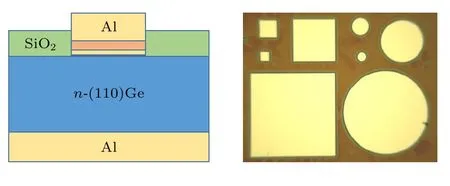

本文采用电阻率为0.05—0.25 Ω·cm 的 n 型(110) Ge 片作为衬底,首先使用循环稀释的氢氟酸 (VHF:=1:100)清洗Ge 片,去除表面原生氧化层.再用等离子增强化学气相淀积在 Ge 上长100 nm 的二氧化硅作为隔离层,接着光刻出图形,用四氟化碳刻蚀暴露的二氧化硅,用电子束蒸发依次蒸镀 1 nm Al 和 10 nm Ni,金属剥离工艺去除不在图形内的的金属,在 350—450 ℃下以99.999%高纯氮气为气氛快速热退火 30 s,再用稀盐酸溶液(VHCl:=1:10)去除未反应的 Ni,接着按照图形进行二次光刻,用电子束蒸发蒸镀 150 nm Al 作为电极.图1 是Ni/Al/Ge SBD 样品的结构图和光镜图.I-V测量使用半导体参数分析仪(KEITHLEY4200) 在 300 K 的黑暗条件下进行.

图1 带有 1 nm Al 中间层的 Ni/Ge SBD 结构图与光镜图Fig.1.Structure and light microscopy of Ni/Ge SBD with 1 nm Al interlayer.

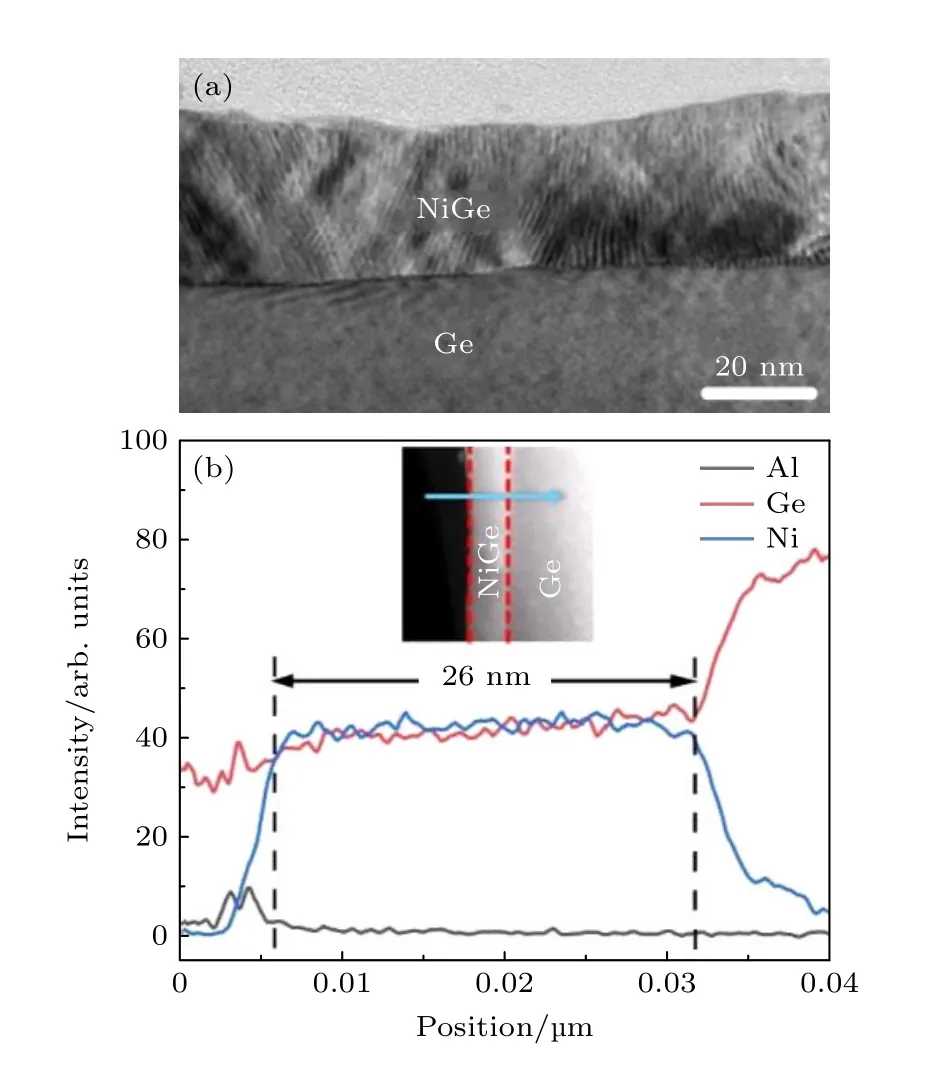

图2 是Ni/Al/Ge SBD 在400 ℃退火后的透射电镜图(transmission electron microscopy,TEM)和X 射线能谱(energy dispersive spectroscopy,EDS).从图2 中可以发现,在使用1 nm Al 插入层调制后,生成了约26 nm 厚的Ni,Ge 原子比为1∶1 的单一的NiGe 相薄膜,此时的NiGe 薄膜连续且均匀,NiGe 薄膜与Ge 衬底界面平整.

图2 Ni/Al/Ge 在 400 ℃ 条件下的 (a) TEM 图;(b) EDS图Fig.2.(a) TEM image of Ni/Al/Ge at 400 ℃;(b) EDS image of Ni/Al/Ge at 400 ℃.

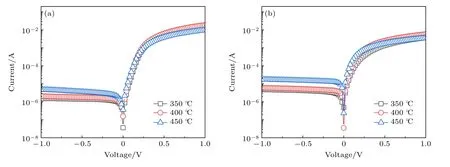

图3 显示了Ni/Ge,Ni/Al(1 nm)/Ge 两种SBDs在 350—450 ℃下的I-V特性.两种肖特基二极管都有明显的整流特性,正向偏置电流的线性区域表明电流满足热离子发射模型.

图3 SBD的 I-V 特性 (a) Ni/Ge;(b) Ni/Al/GeFig.3.I-V characteristics of SBD: (a) Ni/Ge;(b) Ni/Al/Ge.

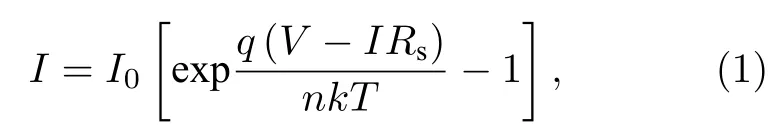

根据热离子发射模型,可以确定 SBD 正向偏置电流I为[12,13]

其中,q为电子电荷;V为外加偏置电压;k为玻尔兹曼常数;T是绝对温度;Rs 是串联电阻;n为理想因子;饱和电流I0可以从lnI与(V-I)的曲线在V=0 时获得,I0为

其中,A为接触的有效面积;A**是理查德常数,对于n型 Ge 来说约等于50 A·cm—2·K—2;ϕB为肖特基势垒,

理想因子n由正向偏置 lnI与V曲线的线性区域的斜率确定,

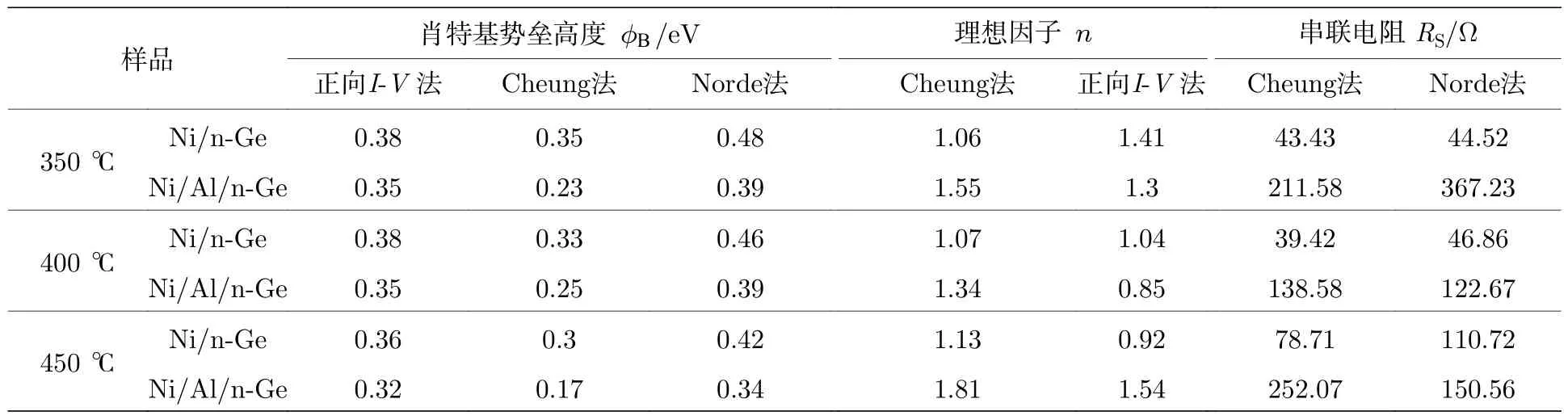

Ni/Ge SBD 的肖特基势垒高度ϕB和理想因子n在 350 ℃ 的时候分别为0.38 eV 和 1.41,在400 ℃ 的时候分别为0.38 eV 和 1.04,在 450 ℃的时候分别为0.36 eV 和 0.92;Ni/Al/Ge SBD 的肖特基势垒高度ϕB和理想因子n在 350 ℃ 的时候分别为0.35 eV 和 1.3,在 400 ℃ 的时候分别为0.35 eV 和 0.85,在 450 ℃ 的时候分别为0.32 eV和 1.54.SBD 的理想因子接近1,说明该结果接近于理想情况.Ni/Al/Ge SBD 的理想因子比 Ni/Ge SBD 的略大,这可能归因于各种影响,包括施加电压的增加导致扩散电流的增加[14],在耗尽区产生复合过程[15],串联电阻Rs 的存在[16],或者是隧穿过程的影响[17].由结果可知 Ni/Al/Ge SBD 的肖特基势垒高度低于 Ni/Ge SBD,这一点在后面讨论.

NiGe/Ge 在450 ℃和Ni/Al/Ge 在400 ℃时提取的理想因子均小于1,可能是俄歇复合效应和正向I-V法选用的是偏低压的原因,从而对于理想因子的计算产生影响.

串联电阻RS、肖特基势垒高度ϕB和理想因子n通过Cheung 的方法由正向偏置I-V数据计算得到,用Cheung 的方法表示含有RS的肖特基接触正向I-V特性的函数为[18]

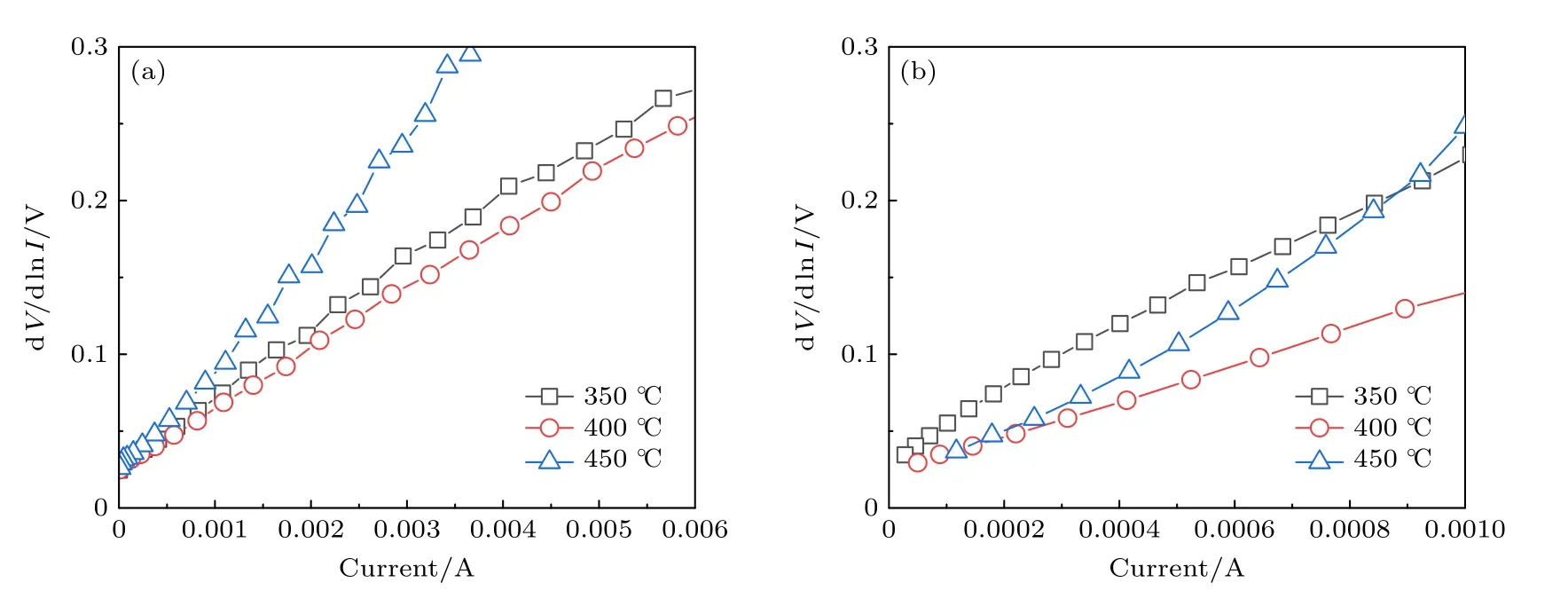

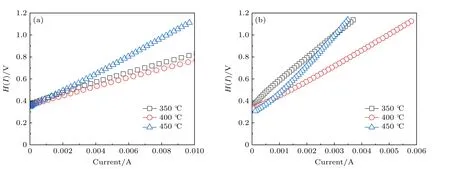

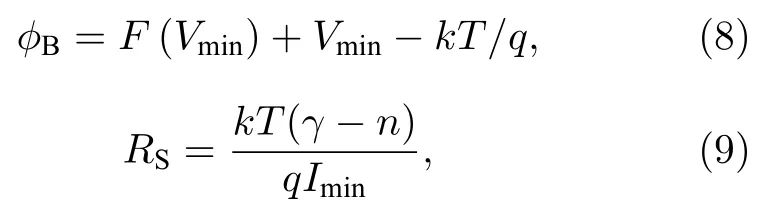

图4 是 Ni/Ge,Ni/Al/Ge SBDs 的dV/d lnI与I的变化曲线,RS和n分别由斜率和y轴截距得到.结果表明,Ni/Ge SBD 的RS和理想因子n在350 ℃ 的时候分别为38.71 Ω 和1.06,在400 ℃的时候分别为37.51 Ω 和1.07,在 450 ℃的时候分别为82.89 Ω 和1.13;Ni/Al/Ge SBD的RS和理想因子n在 350 ℃的时候分别为197.17 Ω 和 1.55,在 400 ℃ 的时候分别为147.64 Ω 和 1.34,在 450 ℃的时候分别为296.77 Ω 和 1.81.图5 是 Ni/Ge,Ni/Al/Ge SBDs的H(I)与I的变化曲线,RS可以由该图斜率得到,ϕB可以由y轴截距和前面得到的n计算得到.结果表明,Ni/Ge SBD 的RS和肖特基势垒高度ϕB在 350 ℃分别为43.43 Ω 和 0.35 eV,在 400 ℃分别为39.42 Ω 和 0.33 eV,在450 ℃分别为78.71 Ω 和 0.3 eV;Ni/Al/Ge SBD 的RS和肖特基势垒高度ϕB在 350 ℃ 分别为211.58 Ω 和0.23 eV,在 400 ℃分别为138.58 Ω 和 0.25 eV,在 450 ℃分别为252.07 Ω 和 0.17 eV.由此可知,使用 1 nm Al 插入层可以降低肖特基势垒高度,但也引入了一定的电阻.

图4 SBDs 的 dV/dlnI 与 I 的变化曲线 (a) Ni/Ge;(b) Ni/Al/GeFig.4.Variation curves of dV/dlnI vs.I for SBDs: (a) Ni/Ge;(b) Ni/Al/Ge.

图5 SBDs 的 H(I )与 I 的变化曲线 (a) Ni/Ge;(b) Ni/Al/GeFig.5.H(I ) vs. I curves of SBDs: (a) Ni/Ge;(b) Ni/Al/Ge.

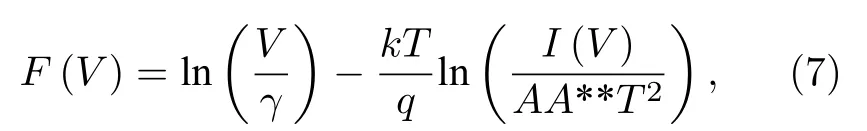

另一种提取肖特基参数RS和ϕB的方法是Norde 的方法,Norde 函数定义为[19]

这里,γ是大于理想系数的任意整数常数,ϕB和RS可以定义为

其中,F(Vmin)和Vmin是曲线F(V)得到的,Imin为电压Vmin处的电流值,n为理想因子.

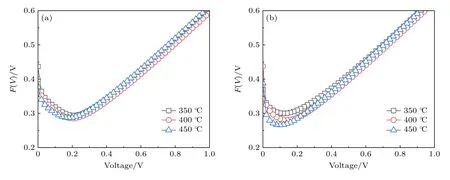

图6为Ni/Ge,Ni/Al/Ge SBDs 的F(V)与V的变化曲线,由公式计算得到的 Ni/Ge SBD 的RS和肖特基势垒高度ϕB在 350 ℃ 时分别为44.52 Ω和 0.48 eV,在 400 ℃ 时分别为46.86 Ω 和 0.46 eV,在 450 ℃ 时分别为110.72 Ω 和0.42 eV;Ni/Al/Ge SBD的RS和肖特基势垒高度ϕB在350 ℃ 时分别为367.23 Ω 和0.39 eV,在 400 ℃ 时分别为122.67 Ω和 0.39 eV,在 450 ℃时分别为150.56 Ω 和 0.34 eV.如表1 所示,利用Norde 的方法得到的与其他方法得到的肖特基势垒高度存在差异,这种差异可能是因为器件与理想热离子偏差有关[20],而且,Norde方法可能不适用理想因子高的整流结,这与热离子发射相悖[21];也可能是由于对正向偏置I-V图不同区域的提取所致,在研究中,正向I-V方法使用了正向I-V特性的低压部分,Cheung 的方法使用了正向I-V特性中的高压部分,而 Norde 方法则考虑了整个正向I-V数据.

表1 不同方法提取的 Ni/Ge 和 Ni/Al/Ge SBDs 的肖特基势垒参数Table 1.Schottky barrier parameters of Ni/Ge and Ni/Al/Ge SBDs extracted by different methods.

图6 SBDs 的 F(V)与 V 的变化曲线 (a) Ni/Ge;(b) Ni/Al/GeFig.6.Variation curves of F(V) vs.V for SBDs: (a) Ni/Ge;(b) Ni/Al/Ge.

4.1 1 nm Al 插入层调制 Ni 与 Ge 的固相反应

在没有 Al 插入层的情况下,Ni 与 Ge 衬底在150 ℃ 退火就开始发生固相反应,生成 Ni5Ge3,在250—600 ℃ 退火温度区间内,NiGe 是唯一的相,在 350 ℃以上退火,NiGe 表面发生团聚效应,导致 NiGe 薄膜不连续[22,23].在有超薄 Al 插入层的情况下(图2),在使用1 nm Al 插入层调制后,此时的NiGe 薄膜连续均匀,生成了单一的NiGe相位.一方面,Al 层可能会减少 NiGe 的生长速率,调制Ni 扩散进入 NiGe/Ge 界面的速率,导致 NiGe 晶粒生成较大的尺寸,就像 Ni-Al-Si 系统中通过 Al插入层调制形成外延 NiSi 层一样[24];另一方面,Al插入层可能减少了 NiGe 晶粒的吉布斯自由能,或者改变了晶界结构从而提高了热稳定性,因为晶界界面能的减小是晶界处发生团聚的驱动力[25].

结合 TEM 和 EDS 测试结果,发现 Al 从插入层转变为了盖帽层.Marshall[26]利用钨标记物研究Ni-Ge 体系中的扩散元素,他们确定Ni为Ni2Ge相中的扩散元素,所以Ni 通过扩散在Al中间层下形成镍锗化物,退火后,大部分 Al 原子从原始层间向表面扩散,形成氧化混合层.根据之前的研究[24,27],使用 Al 插入层用来调节 Ni 与 Si,Ni 与 SiGe 的固相反应,不仅能够获得外延生长的硅镍与锗硅镍薄膜,也都发现了 Al 插入层的“层转移”现象.

4.2 1 nm Al 插入层降低了 Ni/n-Ge 的肖特基势垒高度

在对两种肖特基二极管的I-V特性经过正向I-V法,Cheung 法和Norde 法处理后,发现使用1 nm Al 插入层降低了 Ni/n-Ge SBD 的肖特基势垒高度,这可以从四个方面考虑.

1) 在具有共价键的半导体表面,通常会存在许多未配对电子的原子,称为悬空键,因为Ge 表面存在许多悬空键,所以其表面态密度大[5].Ohta等[28]报道了Al/GeO2的O 会从GeO2向Al 移动并且在界面处形成Al—Ge 键,同时也观察到了Ge表面费米能量的变化.由此可以猜测,使用 Al 插入层减少了 Ge 表面悬空键数量,降低了 Ge 表面态密度,从而有利于降低肖特基势垒高度.2) Liew等[29]报道了使用退火后能与锗形成金属锗化物金属/Ge 的肖特基接触可以调制肖特基势垒高度,因为锗与金属热反应形成埋藏界面,可以极大地调节界面条件.由于锗化物/锗界面是由原子扩散和反应形成的,且Al 可以调节 Ni 与 Ge 的固相反应,由图2 可知,在 400 ℃ 下形成了晶粒连续的NiGe薄膜,NiGe/Ge 界面平整,Al 也从插入层变成盖帽层,因此,可望形成一个“干净”的界面,并修复金属沉积过程中可能造成的损伤.3) Richter 和Hiebl[30]报道了 Al 原子在 NiSi2中可增加 NiSi2的晶格常数,从而使得 NiSi2和 Si 衬底完全匹配.在本研究小组的样品中,虽然 Al 原子含量很少,但是Al 原子的存在可能会改变 NiGe 晶格常数的大小,使得NiGe 和衬底 Ge 的晶格常数正好符合,从而减少了 NiGe/Ge 接触界面因为晶格不连续产生的界面态,降低肖特基势垒高度.4) Sinha等[31]报道了在NiSiGe/SiGe 肖特基结中通过离子注入引入Al 原子,会使得Al 在NiSiGe/SiGe 界面处偏析,因为Al 原子在界面处引入了电偶极子,导致界面处产生一个电场,使得肖特基势垒宽度降低.实验中,大部分Al 原子在退火后由中间插入层转移到表面作为盖帽层,预计也有少量Al 原子可能存在NiGe/Ge 界面,起到调制肖特基势垒的作用.

4.3 1 nm Al 插入层增加了 Ni/n-Ge 的串联电阻

通过dV/dlnI,H(I),Norde 的方法获得的串联电阻可知,在350—450℃下,有1 nm Al 插入层的Ni/n-Ge SBD 引入了一定的电阻.NiGe 通常用于n 型Ge 上的低电阻接触,NiGe/Ge 的电流密度通常为8.9 × 10—3A/cm2,Al/Ge 的电流密度为5.5 × 10—4A/cm2[5].Ghosh等[32]报道 Al/Ge 的接触电阻会随着Al 的厚度而变化,当120 nm 厚的Al 淀积在Ge 形成约 150 nm 的Al/Ge 层时,350 ℃退火后的顶层区域的薄层电阻率为1.5 Ω/m,研磨至裸露Ge 表面时,薄层电阻率可达600 Ω/m.在本实验中,使用的是1 nm Al 作为Ni/n-Ge 的插入层,Al 对NiGe/Ge 界面的调制减少了界面态,降低了肖特基势垒高度,但1 nm Al 与Ge 的相互扩散或许是Ni/n-Ge SBD 串联电阻增大的主要因素.

本文详细研究了Al 插入层对NiGe/n-Ge 接触中电学特性的影响,包括串联电阻、肖特基势垒高度和理想因子等.研究结果表明,1 nm Al 插入层调节后能有效降低 NiGe/n-Ge SBD 的肖特基势垒高度.在Al 元素的调制Ni-Ge 反应过程中,Al 由插入层变为盖帽层.该研究结果对未来 Ge基 MOSFET 源漏接触方面具有一定的参考意义.

猜你喜欢 偏置原子电阻 喷锡钢网曲线偏置方法研究智能计算机与应用(2022年9期)2022-09-28织物电阻测试仪校准中电阻示值测量不确定度评定纺织标准与质量(2022年4期)2022-09-05基于40%正面偏置碰撞的某车型仿真及结构优化汽车实用技术(2022年15期)2022-08-19基于双向线性插值的车道辅助系统障碍避让研究中国信息化(2022年5期)2022-06-13浅谈汽车控制模块中电阻的识读汽车维护与修理(2021年24期)2021-12-23原子究竟有多小?少儿科学周刊·儿童版(2021年22期)2021-12-11原子可以结合吗?少儿科学周刊·儿童版(2021年22期)2021-12-11带你认识原子少儿科学周刊·儿童版(2021年22期)2021-12-11某越野车小偏置碰撞结构优化北京汽车(2021年1期)2021-03-04实现自动控制电阻类型分析之气敏电阻学苑创造·C版(2016年10期)2016-11-19